那么在上述的良率测试、分析和改进过程中,数据是从哪里获取的呢? 在先进的纳米级集成电路技术下,这类数据需要借助专门的成品率测试芯片来提供。 这就像读者和同事们在做一次健康复检。 复检报告不仅包括净高、血糖等明确数据,还包括血液分析得到的循环系统、呼吸系统、免疫系统、B超等复杂数据报告。 、CT、心电图等,图像数据及推论等。

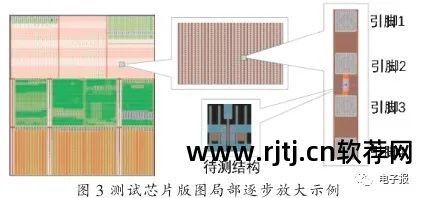

如果把良品率比作集成电路产品和工艺的健康状况,那么集成电路良率测试芯片的作用就是在临床检查实验室中的各种试剂和仪器。 图3是上海光力微电子完成的集成电路成品率测试芯片的版图。 测试芯片上布满了各种测试结构,每个小区域的测试结构大致可以帮助完成一种“体检指标”测试:比如测试某一层的元器件和电路参数(如内部电阻率,阈值电压),检测工艺缺陷(如微图案收缩概率),确定布局设计规则,评估可靠性和制造设备性能等。

图3 测试芯片版图局部逐步放大示例

在临床疑难病症的诊断中,除了常用的测量方法外,医生还会根据患者的特点订购各种专业试剂盒。 在集成电路的设计和制造中,我们也会根据具体的集成电路产品的特性,设计出独特的测试结构,专门用于针对性的良率测试和诊断。

图4为集成电路测试芯片在工艺开发到产品量产过程中三个阶段(工艺开发阶段、试制阶段、量产阶段)的典型应用。

(1) 在新工艺开发阶段,如图4(a)所示,整个晶圆区域用于放置测试芯片,评估工艺步骤中必须控制的关键参数,捕获主要工艺缺陷,以及迅速提高产量。 进入试生产阶段。

(2) 进入试产阶段后,如图4(b)所示,测试芯片将包含更多的测试结构,用于全流程的监控和诊断,以及建立流程/组件模型; 测试芯片与产品密切相关检测手机芯片核数软件,通过并列或嵌入到产品布局中,也可以同步跟踪具体的产品问题。

(3) 在量产阶段,如图4(c)所示,通常会在划片槽内放置代表产品的测试结构,以加强生产品质控制; 传统上晶圆切完后划片槽区就损坏了,现在我就全部用了。 工艺技术进入28纳米以下后,复杂的制造步骤和庞大的布局使得芯片良率更加不可控,因此对良率测试芯片的要求急剧增加,测试芯片中的测试结构数量几乎呈指数级下降。 如何在有限的芯片面积上放置大量的测试结构并快速完成测试已经成为集成电路技术和设计领域最重要的难点之一。

2.可轮询测试芯片

读者从图3可以看出,测试芯片表面放置了一排排测试引脚(焊盘),测试芯片通过引脚与外部测试机热连接。 传统上,测量内阻值需要2个引脚; 要测量晶体管特性,需要 4 个引脚。

如果要回答两个简单的良率测试问题:1)100万个FinFET的阈值电流统计分布的标准误差是多少? 2) 当分两步形成的两条平行金属线相隔 10 纳米时,每 1 亿对中有多少对会收缩? 回答这两个问题分别需要400万和2亿个pin! 而如果芯片表面完全布满测试针,其数量也只能达到1000万颗。

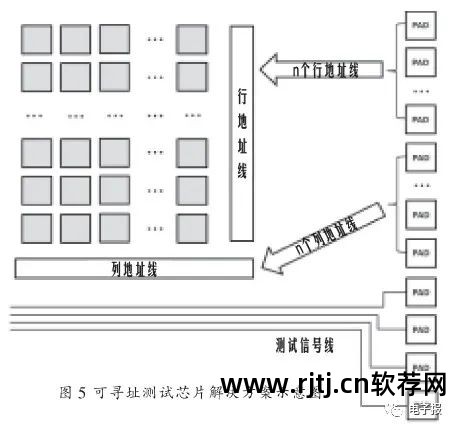

图5是解决上述问题的“可轮询测试芯片”的示意图。

图中左侧是几十个测试引脚,分别将地址线和测试信号线引入左侧测试阵列。 其中,地址线用于选择某个测试结构单元,信号线通过一些选择开关将单元的引出端连接到右侧的测试引脚。 回到上面提出的两个良率测试问题。 理想情况下,20条地址线可以选择220=1024K个FinFET中的一个,加上4条信号线,一共24个管脚可以回答问题1。

问题2:24针也可以用来分别接22条地址线加2条信号线; 这22条地址线用于选择222=4096K个测试单元,每个单元富串联24对平行线(假设在合理范围内出现单挛缩)。

上述可轮询测试芯片的原理看似简单,但在设计和实现上却充满了困难。 首先,测试单元的结构不像是单一的RAM位单元,而是多种多样的,其中有不少是自定义可变参数的PCell批处理实例。

其次,检测精度要求高,信号值可能很微弱。

第三,开关电路和主存储电路的引入引入了相当大的开关内阻和引线内阻。 此外,一些测试结构需要精确的电偏置,一些测试结构具有明显的短路等二阶量,一些测试任务需要使用环形振荡器等有源结构。 因此,需要采用各种电路设计技术来实现系统偏差消除。

由于最先进的产品技术中经常使用小型可轮询测试芯片,掩模和晶圆价格昂贵。 除了保证测试功能和准确性外,在设计和实施时还必须考虑面积、可靠性和冗余度等因素。 根据以上设计目标和约束条件,可轮询测试芯片的设计类似于其他先进集成电路的设计。 它需要用一套完整的、科学的设计方法论来生成一套手工的EDA设计流程。 其主要功能包括测试结构设计、阵列设计、单元布局、信号路由、电路仿真和化学验证等。

3. 测试芯片的手工设计

图6是光力微电子小规模成品率测试芯片的EDA工具和流程图的反例。

在图6中,SmtCell是一个参数化单元格创建工具,可以创建各种类型的参数化单元格。 TCMagic是一个测试芯片的集成设计平台,可以将设计好的SmtCell中的测试结构导出,为设计划片槽和MPW测试芯片提供完整的解决方案。 ATCompiler是一个可轮询测试芯片设计平台,为划片槽中的小型可轮询和可轮询测试芯片提供完整的设计方案。

Semitronix Tester 是一系列用于快速过程监控的专用测试仪,当与可轮询测试芯片结合使用时,可以显着减少热检测时间。 采用多通道并行测试机,实际测试速度可达每小时数亿个测试项目。

DataExp是一款WAT(Wafer Acceptance Test)和测试芯片数据分析工具,用于方便分析检测数据检测手机芯片核数软件,快速制作各种数据分析图表。

DenseArray是一种超高密度测试芯片设计和芯片快速测试IP技术,可以让单个测试芯片容纳数百万个DUT,每秒可以测试数万个DUT,为先进的半导体工艺提供超高元器件开发和良率改进密度芯片架构。

ICSpider是一款基于实际产品布局的手动测试芯片设计工具。 可人工识别和选择FEOL元器件,通过人工绕线实现对实际产品布局环境中大量独立元器件的特性检测。

采用这一整套芯片产品的人工设计流程,就像医生使用量身定做的复检方案,有效实现对症检查。

在某代鞋厂开发新的FinFET工艺中,采用该工艺对工艺开发进程起到了明显的推动作用。 由于流程采用了全新的组件架构,流程风险的准确定位和分析难度很大。 经厂方与光力微电子联合分析,发现需要包含数万个测试结构,采用传统测试芯片方案难度较大。

因此,我们采用了全套的EDA工具流程:首先使用SmtCell生成待测单元的测试结构,然后使用ATCompiler将数以万计的单元和变体单元实例整合到待测单元数组中,然后自动连接定制设计的轮询检测电路,生成高密度的设计版图,最终嵌入到客户的光罩设计中。 相关的选址和测试命令也同时由人工生成,并发送到SemitronixTester设备进行人工测试。

测试结果导出到DataExp后,数据分析完成,形成完整的分析报告。 在项目过程中,根据分析报告,对各工艺方案的选择性试验进行打分,衡量其优劣。 厂方还发现,测试分析推论与其SRAM产品实测良品率几乎完全一致。 完成上述研究过程后,工厂得以迅速调整工艺测试方向,成功解决了工艺缺陷、窗口余量不足、元器件特性偏斜等诸多问题。 它超出了行业预期,并在几个月内达到了 128 Mbit。 芯片良率突破,超出行业预期。

上述整套成品率测试芯片EDA工具及工艺已在多家世界领先的集成电路公司中得到成熟应用,见证了一批批先进集成电路技术和知名芯片产品良率提升的过程。 是目前全球领先的成品率测试芯片解决方案。

4.良率测试大数据的采集、分析与管理

集成电路从设计、制造、测试到被客户使用,不断产生海量数据。 基于大数据技术有效地获取、收集、整理、分析这类数据,不仅是新一代集成电路良率管理系统的目标,也是未来整个集成电路产业向产业升级的关键。 4.0。

良率大数据系统以集成电路良率测试芯片各阶段检测数据为核心,容纳集成电路全生命周期大数据,包括产品数据、工艺数据、生产过程数据、在线检测数据、并使用过程数据。 数据。 同时,这类数据还表现出分布离散、维度多、数据量巨大的特点。 利用机器学习、云计算等人工智能技术,该系统可以有效检测制造过程中的异常情况和其他良率瓶颈,并反馈给制造和设计。

图7 系统采集集成电路制造过程中多点设备数据和检测数据,深入分析良率缺陷复杂的因果关系,成功定位缺陷症结,并通知生产车间对问题进行干预设备(工具)示例。

两个晶圆上小红点的位置分布示例,也可以从图7“机器学习分析与控制系统”下方的晶圆子图中看出; 每个小红点代表通过热参数测试发现的缺陷。

集成电路设计公司和芯片厂在使用良率大数据系统后,可以实现更高水平的良率协同管理。 以“手机中某个芯片在软件系统升级后大约有1%会过热”为例:

(1)设计公司在获取部分问题样品后,根据封装时配置的芯片溯源标签,利用大数据系统对产品封装前后的历史数据进行分析,排除可能的问题源头; 测试数据等信息传输到晶圆厂。 芯片厂在得到设计公司的反馈后,也启动了大数据系统,对晶圆出厂时的检测、各制程阶段的监控等历史大数据进行分析; 对制造过程中的数据进行分析后,数据趋势体现了晶圆的个别静电电压指标。 检测值略高,芯片位置靠近晶圆边缘。 初步怀疑是芯片内部元器件特性导致的问题,于是在这批芯片中追查问题原因。

(2) 借助ICSpider工具设计产品诊断芯片,新的两层掩模可以将产品中频繁出现的大量元器件从产品版图到下方引脚连接起来,并通过实际测量快速芯片测试仪。 将测试结果导出数据分析系统与相关元器件的仿真结果进行对比分析,发现部分元器件的短路情况明显低于模型,其他元器件与模型基本一致,短路路径是从源极到漏极。 将所有元件的设计参数导出到DataExp,进一步发现所有此类高短路元件都具有最小基频-有源区边界距离(minSA); 推测是该类元件与标准型号存在误差,导致部分电路在频繁开启时帧率异常。

(3)针对这个问题,重新设计了一层mask,对此类组件进行特殊修正。 重新纺纱后,在同等使用条件下,产品芯片的帧率大幅提升。 相关风险元器件成为可轮询的电路单元,纳入划线槽工艺监控设计,在后续产品量产中实时监控。 相关的技术经验也在晶圆厂沉淀下来,并带入到日后其他产品的生产和研发中。 从以上例子我们可以看出,更大的数据量、更深层次的数据挖掘方法和先进的数据管理引擎,造就了更强大的良率管理EDA工具系统,可供集成电路设计公司和芯片厂协同使用. 该系统的部分子系统,如支持海量数据扩展的分布式数据平台、支持无晶圆厂设计公司数据分析的网络系统等,已被合作客户使用。 展望不久的将来,业界领先的集成电路设计和芯片工厂可以轻松管理生产过程和产品数据并有效利用,从而在大数据和人工智能时代快速解决以往棘手的良率问题.

杨慎之时政